# Research Accelerator for Multiple Processors

## Architecture, Language and Compiler

Presented 1/8/2007

BWRC Winter Retreat,

Monterey Bay, CA

Greg Gibling (ggdgb@berkeley.edu)

http://www.eecs.berkeley.edu/~ggdgb

http://ramp.eecs.berkeley.edu

Thanks to Krste Asanovic, John Wawrzynek,

Andrew Schultz and Nathan Burkhardt

## Introducing RAMP & RDL

- Research Accelerator for Multiple Processors (RAMP)

A RAMP System is a cross platform architectural simulator.

Designed to foster community research (Share & verify results).

Orders of magnitude faster than existing solutions.

Eases component re-use and integration.

- RAMP Description Language (RDL)

A distributed event & message passing system framework.

The "Target System," the system being emulated, is captured in RDL and emulated on the "Host System," an FPGA or CPU.

Allows virtualization of simulation time to provide cycle accurate simulation results. Compiled by RDLC into Verilog or Java.

- Current Applications of RDL

RAMP Blue: A RAMP System built using Xilinx uBlaze processors on the BEE2

FLEET: A highly concurrent processor architecture focused on comm. not comp.

Overlog/P2: A distributed dataflow description language and execution system

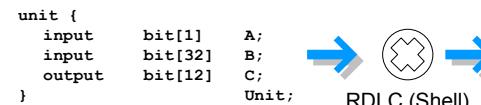

Basic "Target" Model

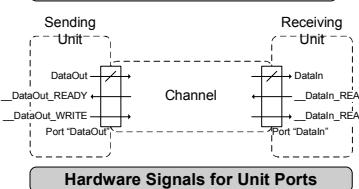

Hardware Signals for Unit Ports

## The "Target" Model

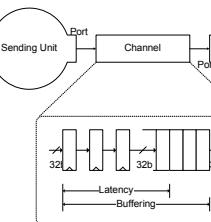

- Units communicate over point-to-point, unidirectional channels

A unit would be ~10,000 gates (Processor + L1 cache)

Units are implemented in the "host" language, eg. Verilog

Existing message passing hardware/software can be ported easily

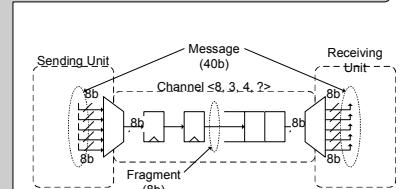

- Channels Delay Model

Allows cycle accurate simulations

Statically typed, variable size messages

Bitwidth (Fragment)

Latency (Both directions)

Buffering

- Benefits

Automatic channel implementation

Ease of unit re-use and sharing

Message Fragmentation

## The Counter Example

```

unit {

input  bit[1]

output bit[32]

}

unit {

output bit[1]

attribute Calinx2

attribute Calinx2

}

Platform specific attributes

(For external connections)

platform {

language

default link

}

map {

platform Calinx2 CounterExample

}

unit {

instance IO: BooleanInput

instance Counter

instance Display7Seg

}

channel fifopipe[1, 1, 1] InChannel

{ BooleanInput.Value -> Counter.UpDown };

channel fifopipe[32, 1, 1] OutChannel

{ Counter.Count -> Display7Seg.Value };

CounterExample;

}

```

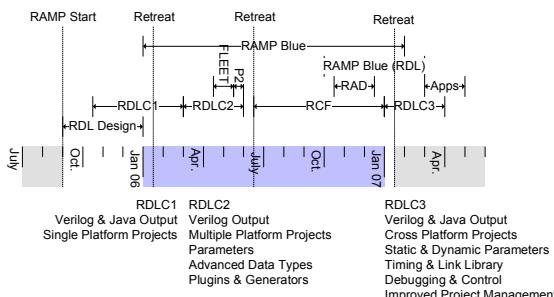

## Timeline

- A simple unit

- No functionality in RDL

RDLC (Shell)

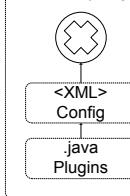

- RDL Hierarchical Netlist

- Include channel model

RDLC (Map)

java Plugins

- Support for multiple target languages

- Automatic cross platform implementation

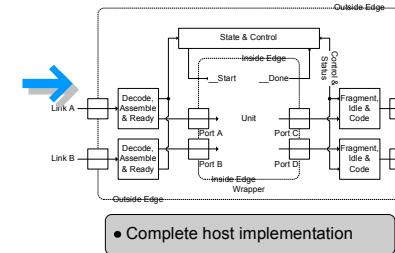

Standard Compiler

- Complete host implementation

Xilinx XUP

Berkeley Calinx2

Any computer

BEE2

## Toolflow